|

Verilog语言要素

|

同其他高级语言一样,Verilog HDL具有自身固有的语法说明与定义格式。下面简单介绍Verilog的语言基本要素。

1.词法

1.1 空白符与注释

在Verilog语言中,空白符与注释和C语言相同。Verilog HDL的空白符包括空格(\b)、换行符(\n)及换页符。在Verilog HDL中有两种形式的注释:

/*第一种形式:可以扩展至多行 */

//第二种形式:在本行结束。

1.2 数字与字符串

由于Verilog HDL语言只用于描述数字系统,因此Verilog HDL语言中常量(信号)的取值通常由以下4种基本的逻辑状态组成:

1) 0:低电平、逻辑0或“假”;

2) 1:高电平、逻辑1或“真”;

3) x或X:未知状态,可能是0,也可能是1或z;

4) z或Z:高阻态。

Verilog HDL中有3种类型的常量:整数、实数和字符串。

1.3 标识符

Verilog HDL中的标识符可以是任意一组字母、数字、$符号和_(下划线)的组合,但标识符的第一个字符必须是字母或者下划线。另外,标识符是区分大小写的。

1.4 运算符

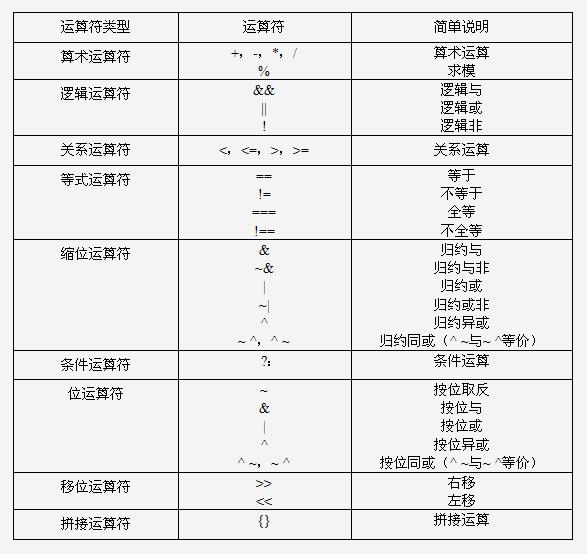

Verilog语言参考了C语言中大多数算符的语义和句法,提供了功能丰富的运算符。按功能不同可分为算术运算符、逻辑运算符、关系运算符、等式运算符、缩位运算符(又称归约运算符)、条件运算符、位运算符、移位运算符和拼接运算符9类。表7.1给出了Verilog HDL中定义的运算符分类及简单功能说明。

2.数据类型

Verilog HDL定义了多种数据类型,这里,主要介绍连线型(wire)、寄存器型(reg)和整形(integer)。

2.1 连线型

Verilog HDL提供了多种连线型变量,最常用的是wire连线型变量。

wire型变量的格式:

wire[n-1:0] 数据名1,数据名2,……数据名i;//共有个i数据,每个数据位宽n

或:wire[n:1] 数据名1,数据名2,……数据名i;

2.2 寄存器型

常用的寄存器数据类型的关键字是reg。

reg型变量的格式:

reg[n-1:0] 数据名1,数据名2,……数据名i;

或:reg [n:1] 数据名1,数据名2,……数据名i;

|

|

|